Western Digital has developed four RISC-V cores, the 64 bit, multicore SweRV Core EHX3 and three 32 bit cores, the SweRV Core EH1, EH2 and EL2.

The SweRV Cores will be used in a variety of Western Digital products in the near future. The 32 bit cores have been open sourced in CHIPS Alliance github.

CHIPS Alliance is an organization that develops open source hardware and open source software design tools. It is a barrier free, collaborative environment which lowers the cost of RTL development.

The following cores are available from Western Digital, some of them are readily available for download while the rest may require licensing.

SweRV Core EHX3

SweRV Core EHX3 is a 64 bit, multi core capable, 9 stage pipeline core.

SweRV Core EHX3 Architecture

SweRV Core EHX3 multi core implementation with Tilelink.

SweRV Core EH1

The Western Digital SweRV Core EH1 is a 32-bit, 2-way superscalar, 9 stage pipeline core.

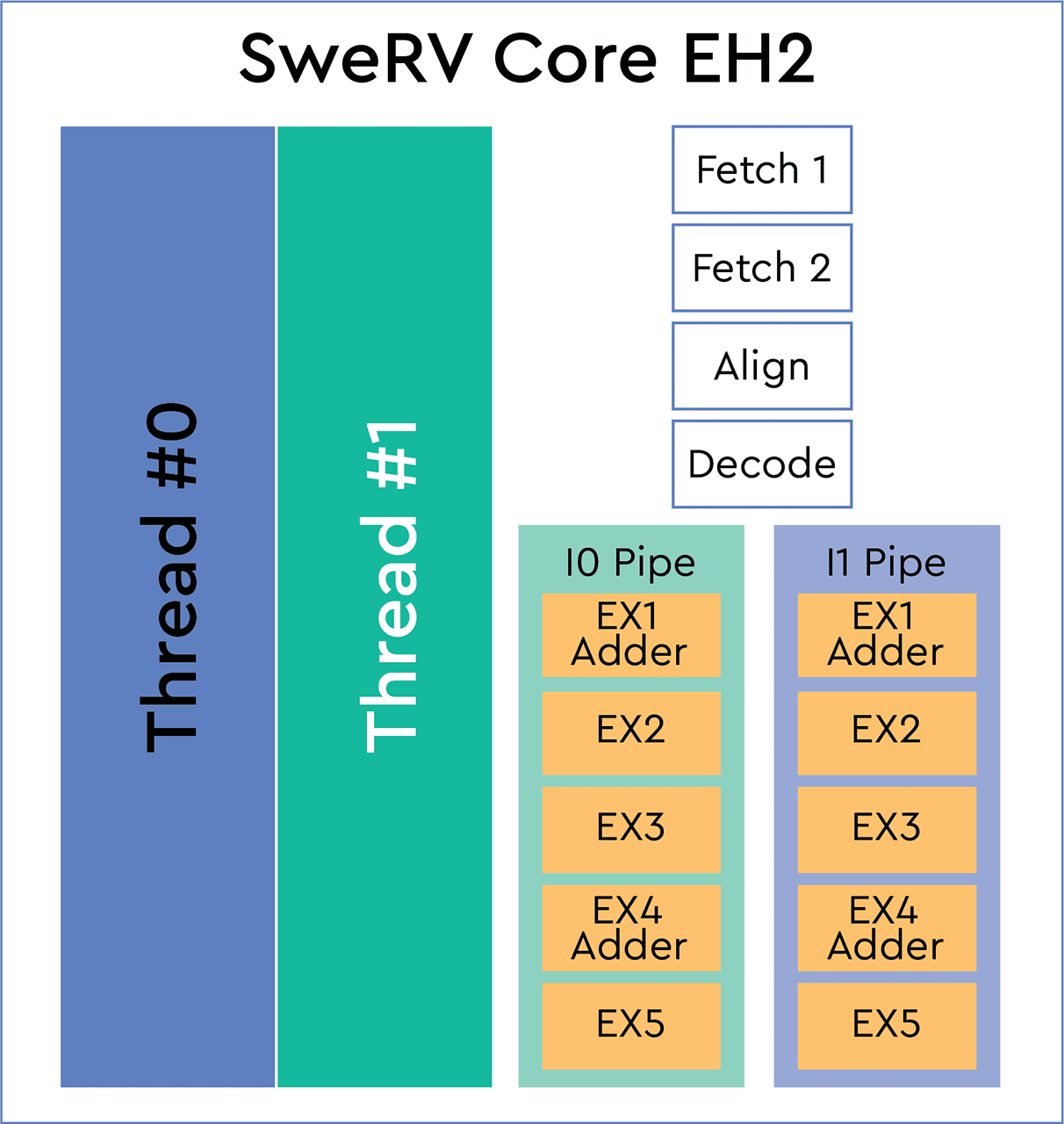

SweRV Core EH2

The SweRV Core EH2 was built off of the EH1, but adds dual threaded capability for additional performance.

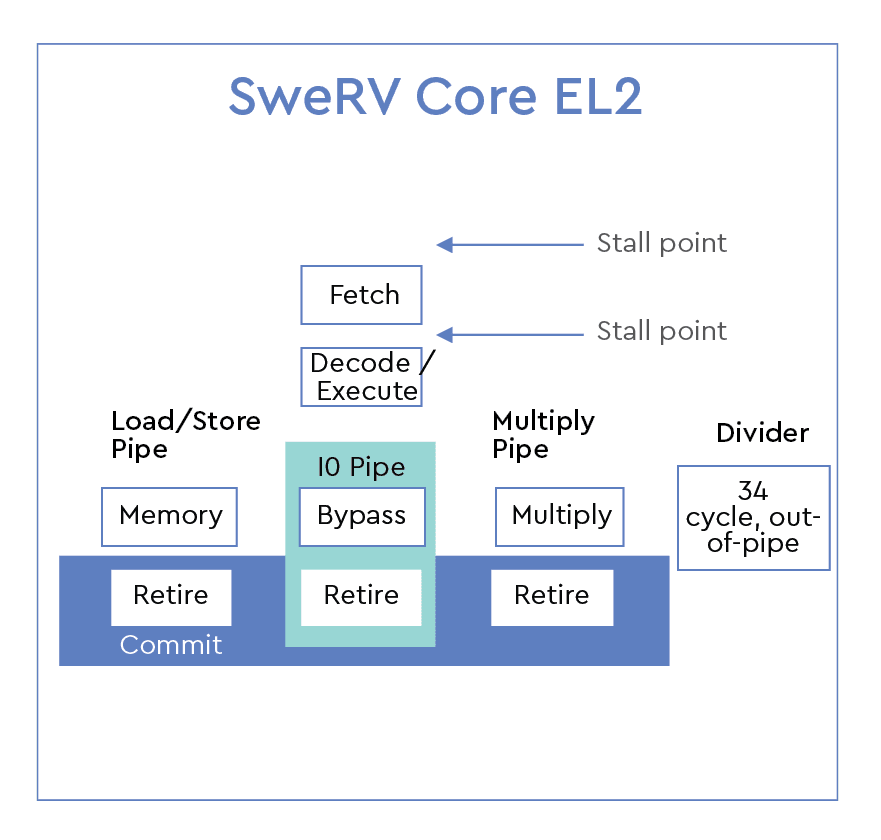

SweRV Core EL2

The SweRV Core EL2 is a smaller core with moderate performance. It was designed to replace state machines and other logic functions in SoCs.

You can download the Western Digital RISC-V cores here

Leave A Comment

You must be logged in to post a comment.